# HEWLETT-PACKARD JOURNAL

**MARCH 1987**

# HEWLETT-PACKARD JOURNAL

March 1987 Volume 38 • Number 3

#### **Articles**

4 Hardware Design of the First HP Precision Architecture Computers, by David A. Fotland, John F. Shelton, William R. Bryg, Ross V. La Fetra, Simin I. Boschma, Allan S. Yeh, and Edward M. Jacobs The CPU is TTL, the memory is 256K DRAMs, and the processor pipeline executes an instruction every 125 ns.

18 An Automated Test System for the First HP Precision Architecture Computers, by Thomas B. Wylegala, Long C. Chow, and Randy J. Teegarden The test system requires minimal cooperation from the unit under test.

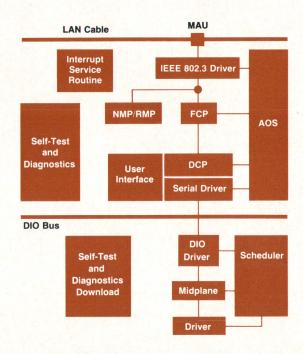

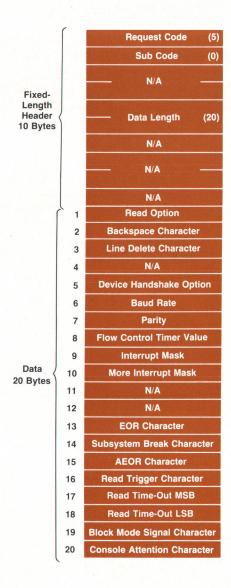

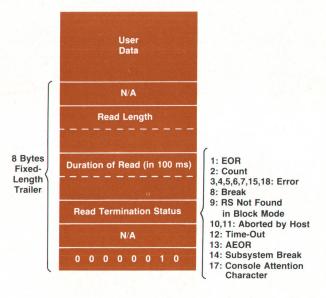

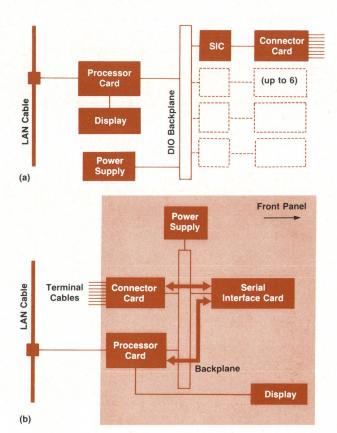

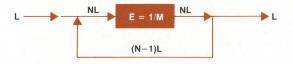

A Distributed Terminal Controller for HP Precision Architecture Computers Running the MPE XL Operating System, by Gregory F. Buchanan, François Gaullier, Olivier Krumeich, Eric Lecesne, Jean-Pierre Picq, and Heng V. Te The DTC not only saves space in the SPU cabinet, but also offloads the character-oriented tasks from the host computer.

29 Hewlett-Packard Precision Architecture Compiler Performance, by Karl W. Pettis and William B. Buzbee Here's how the combination of a RISC architecture and optimizing compilers can outperform CISC machines.

38 Viewpoints—A Viewpoint on Calculus, by Zvonko Fazarinc Should the infinitesimal calculus be taught at all?

#### **Departments**

- 3 In this Issue

- 3 What's Ahead

- 35 Authors

#### In this Issue

This issue continues our series on HP Precision Architecture topics. On page 4 you'll find the hardware design story of the first two members of HP's new generation of computers based on HP Precision Architecture. The HP 9000 Model 840 Computer runs the HP-UX operating system and is designed for technical and real-time applications. HP-UX, HP's version of AT&T's UNIX® System V operating system, was featured in our December 1986 issue. The HP 3000 Series 930 runs the MPE XL operating system and is designed for business data processing. We've received a paper on MPE XL and will be publishing it later this year. Both the Model 840 and the Series

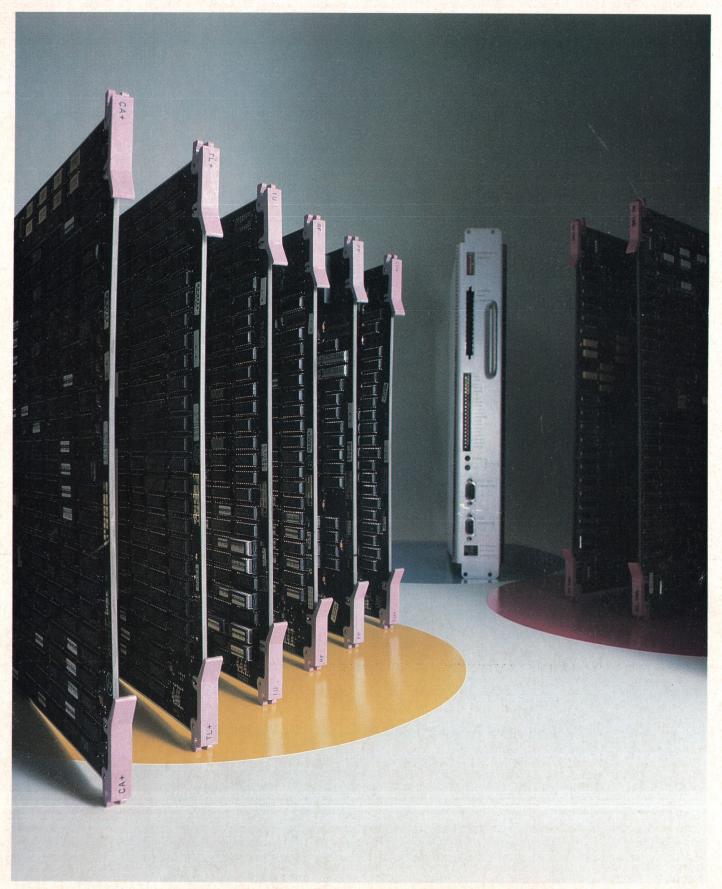

930 have the same processor, which is noteworthy because it uses a relatively old-fashioned integrated circuit technology, TTL, and yet achieves about four times the speed of the fastest of HP's previous-generation computers. It was, of course, this potential speed of RISC-like architectures (RISC means reduced instruction set computer) that triggered the development of HP Precision Architecture. Future computers implementing the architecture in state-of-the-art VLSI technology are expected to be even faster. The Model 840/Series 930 processor is the six smallest boards on this month's cover. The two larger boards are an 8M-byte memory module and the board with the handle is the system monitor.

HP Precision Architecture is more than just a RISC architecture. For any architecture, compilers must be developed to provide a high-level language interface to the machine. Whether the speed potential of a RISC architecture is realized, particularly for commercial languages requiring many complex operations, is largely a function of compiler design. How the HP Precision Architecture compiler designers approached some of the more challenging problems is detailed in the paper on page 29, which also gives performance data showing how well they succeeded in solving these problems.

The HP 3000 Series 930 can have a large number of terminals connected to it through intelligent hardware modules called HP 2345A Distributed Terminal Controllers, each of which accommodates 48 terminals. The theory, design, and operation of the DTC are described in the article on page 21. Queueing theory was used to predict its performance. On page 18 is a description of the production test system for the Model 840 and Series 930 computers.

I can't remember ever having anything controversial in these pages, so the Viewpoints article on page 38 may be the first time. It's a paper presented to the Mathematics Panel of the American Association for the Advancement of Science by Zvonko Fazarinc of HP Laboratories. We hope you'll find his ideas on the teaching of infinitesimal calculus thought-provoking.

-R. P. Dolan

#### What's Ahead

Next month's issue will feature the design of the HP 8175A Data Generator and its arbitrary waveform generator option. There will be two research reports, one on software reliability and one on surface mount solder joint failure modes. Another paper will discuss the design and application of HP's PL-10 software package, a master planning tool for the semiconductor manufacturing industry.

### Hardware Design of the First HP Precision Architecture Computers

The HP 3000 Series 930 and the HP 9000 Model 840 are implemented with commercial TTL logic.

by David A. Fotland, John F. Shelton, William R. Bryg, Ross V. La Fetra, Simin I. Boschma, Allan S. Yeh, and Edward M. Jacobs

HE HP 9000 MODEL 840 and the HP 3000 Series 930 are the first technical and commercial computer products, respectively, to use the new Hewlett-Packard Precision Architecture. HP Precision Architecture combines a simplified, RISC-like instruction set with a powerful coprocessor architecture, a 64-bit virtual memory addressing system, a new high-performance I/O architecture, and provision for multiprocessors.

The HP 9000 Model 840 and the HP 3000 Series 930 are both based on the same processor, memory system, and I/O system. The processor consists of five printed circuit boards, each 8.4 by 11.3 inches, containing off-the-shelf TTL logic. It uses FAST™ TTL, 25-ns and 35-ns static RAMs, and 25-ns and 35-ns PALs™. These five boards include the processor pipeline, which fetches and executes an instruction every 125 ns, a 4096-entry translation lookaside buffer (TLB) for high-speed address translation,

FAST is a trademark of Fairchild Camera and Instruments Corporation. PAL is a registered trademark of Monolithic Memories.

and 128K bytes of cache memory. An additional (sixth) board contains the hardware floating-point coprocessor. Each board contains about 150 ICs.

A 20-Mbyte/s bus called the MidBus connects the CPU, main memory, high-speed I/O cards, and I/O channels. There are six memory slots, and memory comes in two-board 8M-byte sets. This gives a maximum of 24M bytes of memory. Memory uses 256K-bit nibble-mode dynamic RAMs with single-bit error correction and double-bit error detection. There are seven general-purpose I/O slots, which can be used for high-speed I/O cards or I/O channels. The I/O channel is a two-board set. Most I/O is handled by cards on an HP CIO bus connected to the MidBus through an I/O channel. The HP CIO bus is a 5-Mbyte/s I/O bus.

A system monitor card monitors power supply levels and temperature and provides front-panel functions and system overtemperature shutdown. An access port card allows remote field support access for diagnosis.

The differences between the HP 9000 Model 840 and the

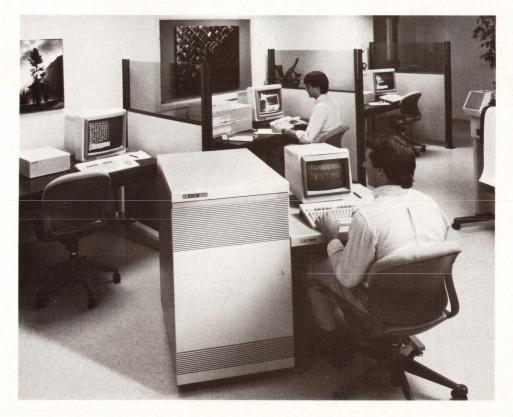

Fig. 1. The HP 9000 Model 840 Computer is the first HP Precision Architecture computer for technical and real-time applications. Its operating system is HP-UX, HP's version of AT&T's UNIX System V operating system.

HP 3000 Series 930 are in configurability and software. The HP 9000 Model 840 (Fig. 1) is a technical machine. It runs HP-UX, HP's version of AT&T's UNIX® System V operating system with real-time extensions.³ The Model 840 is a single-bay, one-meter-high system. Its input/output system has one HP CIO channel, and up to 12 CIO cards. Terminal I/O is done using a six-port multiplexer card, limiting the number of terminals to sixty. 8M bytes of memory is standard.

The HP 3000 Series 930 (Fig. 2) is a business machine. It runs MPE XL,<sup>4</sup> a new version of HP's proprietary MPE operating system, and provides compatibility for existing HP 3000 customers. The Series 930 has two one-meter-high bays to provide more I/O capacity. It has three CIO channels, and 16M bytes of memory is standard. The second bay contains two CIO buses and up to two HP 2345A Distributed Terminal Controllers.<sup>5</sup> Terminal I/O for MPE XL is done using an IEEE 802.2 local area network and the HP 2345As, each of which can handle up to 48 terminals and can be located near a work group using a LAN cable.

#### **History of the Project**

Development of HP Precision Architecture began at HP Laboratories in early 1982. The processor instruction set and virtual memory system were well-defined by the end of 1982. The TTL implementation project began in April 1983.

The project's goals were low factory cost, good performance, and very fast design time, since this was to be the software development machine for the HP Precision program. We used internal HP design tools for schematic cap-

UNIX is a registered trademark of AT&T.

ture and timing analysis, and FTL, a simulator developed at Amdahl Corporation, for gate level simulation of the entire system. We did not build wirewrap breadboards, but went straight to printed circuit boards.

Simulation of the processor started in the fall of 1983, and we had working processors by early 1984. A complete processor with cache, TLB, and main memory was delivered to the software developers in July 1984. This version of the machine did not have an I/O channel or a hardware floating-point coprocessor since the architectures for these units were not complete. I/O was done with a parallel interface to an HP 9000 Series 200 Computer.

This machine was sufficient for software development, and we built 36 of them over the next five months. This version used bench power supplies and had a very small cabinet. It ran at 30 MHz, rather than the 32 MHz of the final machine. Over the next six months the final cabinet, power system, and system monitor were designed and the I/O channel was completed.

In January 1985 we put together our first lab prototype system. This system looked very much like the final product. It had working I/O channels, up to 24M bytes of memory, and a full-speed processor. Between January and September we built almost 200 for use as software development machines. This machine had only 32K bytes of cache memory and a 1024-entry TLB. It could execute about 3.5 million instructions per second (MIPS).

Enhancements were added for higher performance and better manufacturability during 1985. Newer, denser static RAMs were available, so we quadrupled the size of the caches and TLBs. Some other minor changes were made to eliminate bottlenecks in the processor and the final performance rating is 4.5 MIPS. We also completed the design

**Fig. 2.** The HP 3000 Series 930 Computer is the first HP Precision Architecture computer for commercial applications. Its operating system is HP's proprietary MPE XL.

of the floating-point coprocessor, and started building fullfunctionality production prototypes in May 1986. The first production Series 840 was shipped in November 1986.

#### **CPU Design**

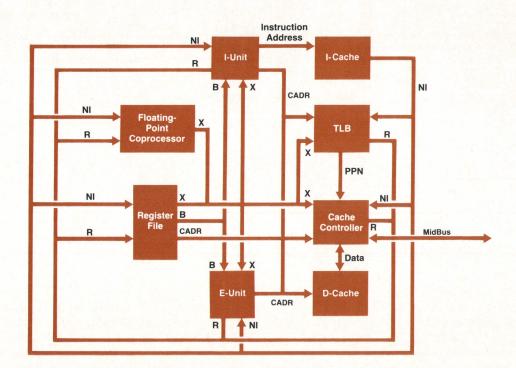

The simplicity of HP Precision Architecture allowed the entire CPU and floating-point coprocessor to be implemented on six medium-size boards, even though it was designed using mostly MSI TTL, a technology with a fairly low level of integration. These six boards and the six major buses internal to the CPU are organized as shown in Fig. 3.

#### **Instruction Unit**

The I-unit (instruction unit) controls the flow of instructions. It executes branch instructions and handles traps and interrupts. The I-unit also creates and distributes the system clocks that keep all of the elements of the processor synchronized. Instruction execution begins when the I-unit creates the address of the instruction to be executed and sends this address to the I-cache, which contains the instructions to be executed. The I-cache sends the instruction back on the NI (next instruction) bus, which is distributed to all of the processor boards.

Instruction decoding is decentralized, with each board decoding only as much of the instruction as is necessary for that board to do its job.

#### **Register File Board**

The register file board supplies the operands (the values to be operated on) for the instruction. It maintains thirty-two general registers. Each register is thirty-two bits wide. In addition, the register file maintains copies of the twenty-five control registers specified by HP Precision Architecture.

In many computer architectures, operands can be stored

in memory. In HP Precision Architecture, all operands are stored in the general registers or encoded in the instructions. The only instructions that access data memory are load instructions and store instructions. The addresses for the load and store instructions are created from values in the general registers and from values encoded in the instructions.

The register file board drives the register values out to the rest of the CPU on the X (index) and B (base) buses. Sometimes in a pipelined implementation like the Model 840/Series 930 processor, a result being created by one instruction or data being loaded from memory is needed immediately by the following instruction before there is time to store the result or the data into a general register. The register file board recognizes these cases and routes the data around the general registers to the instruction that needs it.

#### **Execution Unit**

The E-unit (execution unit) performs arithmetic calculations on the operands. It executes the arithmetic instructions and creates the addresses for load and store instructions. It contains a 32-bit ALU (arithmetic logic unit) for arithmetic and logical calculations, a barrel shifter for shift instructions, and complex mask/merge circuitry for extracting and depositing bit strings. It also contains a preshifter on one input to the ALU. This is used in address calculations and for special instructions used in software multiply routines (the Model 840/Series 930 does not execute multiply instructions directly in hardware.)

The E-unit sends its result back to the register file over the R (result) bus. If the instruction is a load or store instruction, then the address is sent to the cache controller and TLB boards on the CADR (cache address) bus. The E-unit also creates a condition code based on its result. That condition code is sent to the I-unit to be used for conditional

**Fig. 3.** Block diagram of the CPU for the HP 9000 Model 840 and HP 3000 Series 930 Computers.

branches and conditional skips.

#### TLB, Cache, and Coprocessor

The TLB (translation lookaside buffer) controls the access to virtual memory. HP Precision Architecture provides a very large global address space. Addresses in the Model 840/Series 930 processor are 48 bits long. The architecture will support up to 64-bit addresses. This huge address space increases performance by making memory management easier in both software and hardware. However, it would be impossible to support that much physical memory, so it's necessary to translate the large virtual addresses into smaller physical addresses.

The TLB performs this translation from the virtual memory address (the address that the processor sees) to the physical memory address (the address that the memory system sees). It also keeps track of protection information (i.e., which user is allowed to access which portions of virtual memory).

The large global virtual address space specified by the architecture allows effective use of a TLB with many entries. The Model 840/Series 930 TLB has entries for 4096 pages of virtual memory. Each page contains 2K bytes of code or data. This is an enormous number of entries compared to other computers, and makes the performance penalty for the virtual-to-physical translation very small (the penalty comes from the processing necessary when the TLB does not contain an entry for the virtual memory page that the processor is trying to access.)

The cache controller manages two high-speed cache memories, one for code and one for data. In other architectures, caches, if they are used, are forced to be transparent, that is, invisible to the software. HP Precision Architecture allows explicit software management of the caches, thereby making it possible to separate the code and data caches, doubling the available bandwidth between the caches and the rest of the processor.

The floating-point coprocessor works in parallel with the main processor to do floating-point calculations. This allows the processor to continue processing during the several cycles that it may take for the floating-point coprocessor to complete the execution of a floating-point instruction.

#### **Architectural Impact**

Because the architecture is simple and regular, it allows for a nonmicrocoded implementation such as this one. This means that the implementation is a fairly straightforward interpretation of the architecture, and architectural features have a large impact on the processor organization.

For example, all instructions are exactly 32 bits in length. Most instructions use one or two general registers as operands, and the register addresses of these operands are always encoded in the same place in the 32-bit instruction. This means that prefetching of the instruction and its operands can be done without regard to the decoding of the instruction or to the execution of the previous instruction.

As the instruction comes out of the cache and is distributed to the processor boards, the register file board receives the instruction from the NI (next instruction) bus. The register file board immediately prefetches from the register

file the two operands necessary for the instruction, so that at the beginning of the next cycle, when the rest of the processor is prepared to execute the instruction, the operands have already been obtained and are ready to be driven out to the rest of the processor on the X and B buses.

Because of the simplicity of the instruction encoding, it was very efficient to distribute the instruction decoding among all of the processor boards, with each board decoding only the piece of the instruction that applies to that board. Each board, then, receives the instruction from the NI bus as it comes out of the cache and prepares to execute it during the following cycle.

Because the architecture relies so heavily on register values for operands, the register file is central to the instruction flow. Each instruction begins with the prefetching of the instruction from the cache and the prefetching of the operands from the register file. From here, the operands fan out to the rest of the processor, which consists of several short, parallel data paths.

This, again, is a result of the architecture, which heavily emphasizes these short, parallel data paths as a means of increasing performance. The E-unit, for example, has a barrel shifter combined with sophisticated mask/merge circuitry for bit manipulation. It also contains a 32-bit ALU. The results from these two pieces of circuitry are never needed in the same instruction, allowing them to be placed in parallel so that neither one will impact the speed of the instructions that use the other.

The I-unit can calculate branch target addresses in parallel with E-unit calculations, which allows for instructions that calculate an arithmetic result and conditionally branch based on that result, all in one cycle. This makes possible very efficient loops and range checking in the code.

Another example of the parallelism encouraged by the architecture can be found in the cache and TLB. Because the architecture does not permit one physical address to be referenced by more than one virtual address, the cache and TLB accesses can be done in parallel. At the same time that the TLB is performing the translation from virtual to physical address, the cache is obtaining the data (or code), and reading a tag that indicates which physical address that data belongs to. When the TLB has completed the translation, the physical address is sent to the cache over the PPN (physical page number) bus, and compared to the physical address that the cache has read from its tags to determine whether this data is really the data that is needed. In most architectures, these two processes must be done serially, resulting in a much longer cache access time.

#### **Processor Pipeline**

The processor is pipelined. This means that several instructions are in various stages of execution at any one time. Whereas this implementation technique must be made transparent in most architectures, it is supported, and in fact encouraged, by HP Precision Architecture.

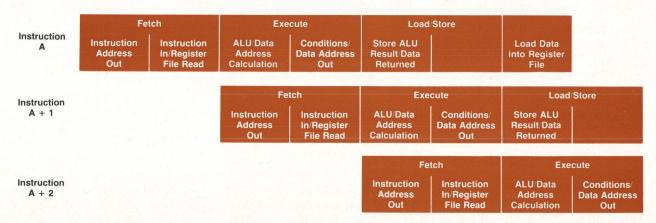

The pipeline has three stages, as shown in Fig. 4. Each stage takes 125 ns, and is subdivided into two minor stages. The first stage is referred to as the fetch stage. During the first half of this cycle the address of the instruction is sent to the instruction cache from the I-unit. During the second

half, the instruction is returned and distributed, instruction decoding is begun, and the register operands are read out of the register file.

The second stage is referred to as the execute stage. It is during the first half of this stage that the arithmetic result is calculated if this is an arithmetic instruction, or the data address is calculated if this instruction is a load or store instruction. If this is a branch instruction, the branch target address is also calculated during the first half of this stage. For arithmetic instructions and for conditional branch instruction, the condition is calculated during the second half of this cycle. For loads and stores, the second half of the cycle is used to drive the data address to the cache controller and the TLB.

Notice that if the instruction is a branch instruction, because of the pipeline the following instruction is being fetched while the branch target is being calculated. In most architectures, this would result in an instruction being fetched that was not going to be executed, and would result in a wasted cycle with every branch. In HP Precision Architecture, branches are delayed by one instruction. In other words, one additional instruction is executed after the branch instruction before the branch target is reached. This is an example of how the architecture supports pipelined implementations, resulting in a performance improvement over traditional architectures.

The third pipeline stage is referred to as the load/store stage. During this stage, load data is returned from the cache, or stored data is written to the cache. It is during the first half of this stage that the E-unit result is actually written into the register file, and during the first half of the following cycle that the load data is written into the register file. Notice that the register file is only written during the first half of any cycle. This is because during the second half cycle it is necessary to read from the register file the operands being used by the instruction that is currently in its fetch stage.

#### Cache and TLB Design

The cache and TLB (translation lookaside buffer) speed up memory accesses by keeping recently accessed data and virtual address translations in local high-speed memory. They are designed to give the best performance without increasing the CPU's basic cycle time. They take advantage of the architecture, which allows a simple design, and they are pipelined to get increased bandwidth without increased hardware.

The cache is a high-speed memory that shortens typical main memory access times by keeping copies of the most recently accessed data. The cache is divided into a 64K-byte instruction cache and a 64K-byte data cache, each of which is divided into 4096 16-byte blocks. Each block has an address tag that specifies the block of memory from which it came. When the processor accesses data or instructions, the block is copied from main memory into the instruction or data cache, as appropriate. All further references use the copy in the cache, until the cache block is needed for a different block from memory. At that point, the block that is removed is written back to memory only if it has been modified by the processor.

Similarly, the TLB speeds up virtual address translations by acting as a cache for recent translations. Both virtual memory and physical memory are divided into pages of 2K bytes, and each TLB entry maps a virtual page number to a physical page number. Each virtual address is made up of a virtual part (i.e., the virtual page number) and a physical part (i.e., the offset within the page). The TLB translates the virtual page number to get a physical page number. This is concatenated with the page offset to generate the physical address.

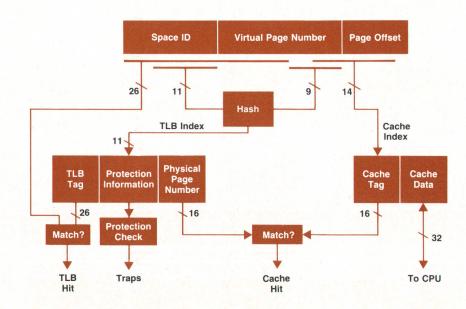

To allow the implementation of large, high-speed caches, HP Precision Architecture disallows address aliasing, that is, the capability of having two different virtual addresses pointing to the same physical location. This allows the Model 840/Series 930 processor to access the cache and TLB in parallel, without the problems and constraints this has had in other architectures. Thus, the access time is the worst of the TLB and cache access times, rather than the sum of them (see Fig. 5).

#### **TLB Operation**

The virtual memory space is divided into virtual pages of 2048 bytes each. A data structure in main memory called the page table keeps information about each virtual page that is currently in use (i.e., a copy of that page exists in the physical memory). This table has one entry for each virtual page, and contains information on the protection

Fig. 4. CPU pipeline.

of that page (which users are allowed what kind of access to the page) and the physical page number of that page (where the page exists in physical memory).

The TLB acts as a cache for this information. Just as the instruction and data caches keep copies of recently accessed memory locations, the TLB keeps copies of the information for recently accessed pages. The Model 840/Series 930 TLB has entries for 4096 pages, 2048 for code and 2048 for data.

With each memory access (both instruction fetches and data loads and stores), the TLB checks the protection information for that page and the physical address of that page. It sends the physical address to the cache, so that the cache can check to see if the word being accessed is contained in the cache. If the protection information indicates that the user is not allowed the kind of access being attempted, the TLB signals the register file board to back out of the instruction and signals the I-unit to raise a trap.

TLB miss handling is done in software on the Model 840/Series 930. This means that if none of the entries in the TLB corresponds to the virtual address being accessed, a trap is raised. Software must then get the information about that page from the page table, place it in a TLB entry, and reexecute the instruction.

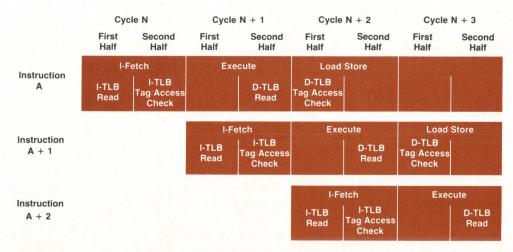

The TLB is pipelined so that it can perform both an instruction address translation and a data address translation each cycle. The first half of every cycle, it reads the tag and translation out of the TLB for the instruction being fetched (see Fig. 6). During the second half of the cycle, it checks the tag for a match (also known as a hit) and performs a protection check.

Also during the second half of each cycle, the tag and translation are read out of the TLB for any memory access instruction currently in the execute phase. This is checked for a match and protection during the following half cycle, that is, the first half cycle of that instruction's load/store phase. Thus, each half cycle the TLB starts a new translation, which will be completed one cycle later.

The TLB is a direct mapped TLB. It has 2048 entries for instructions and 2048 entries for data. Direct mapped

means that each virtual page translation can exist in only one entry of the TLB, and if a program accesses another page that maps to the same entry, the first one is replaced. Although direct mapped TLBs (and caches) have greater miss rates than set-associative TLBs of the same size, the direct mapped TLB minimizes cycle time, which has a greater impact on performance.

The TLB is addressed by the 9 LSBs of the virtual page number hashed with the 11 LSBs of the space ID to create an 11-bit index. The hash takes the two LSBs of the space ID, then flips the next 9 bits of the space ID around and exclusive-ORs them with the 9 LSBs of the virtual page number. In addition, one address bit selects instruction or data, since the TLB is split for instruction and data accesses, although these use the same hardware. The address hash reduces the likelihood of a program's heavily using a single TLB entry for two different pages. In addition, the large size of the TLB greatly reduces overall miss rates.

In addition to the physical page number of the page translated and a virtual tag to identify the corresponding virtual page, each TLB entry has extra information to implement the HP Precision protection scheme. This includes an access rights field, an access ID, and several status bits. The access rights field specifies how the page can be used (e.g., read only, read/execute, etc.) and the necessary privilege level to use it. The access ID is a key that must match one of the four protection IDs (in control registers) that processes can have, in addition to the access rights check. The status bits include an entry valid bit, a dirty bit, two different break-on-access bits, and an I/O bit which marks whether the page corresponds to an I/O module.

Since TLBs do not contain the translations for all pages in memory simultaneously, they occasionally do not have the desired translation and a miss occurs. The instruction cannot complete without the translation, so the TLB causes a trap. This causes the current processor state to be saved in control registers, and execution continues in the software TLB miss handler. If the page is actually in memory, the handler will insert the needed TLB entry and retry the offending instruction. If the desired page is not in memory

Fig. 5. Cache/TLB block diagram.

(i.e., on disc), the handler will invoke the page fault handler. Because the instruction is restarted after a TLB miss, a TLB must be able to contain two arbitrary translations to be able to complete any instruction, one to fetch the instruction and one to access data requested by the instruction (if load or store). If it cannot, there are cases where the program will get stuck first replacing the entry for fetch, then for data, and back again. Hence the TLB is split, half for instructions and half for data, to guarantee forward progress.

One side effect of the very large HP Precision address space, 256 terabytes (2<sup>48</sup> bytes) in this case, is that all processes execute in the same unified address space. This allows different processes (or programs) to share code or data more simply, since the addresses are the same. Also, since there is only one address space (as opposed to separate address spaces for each user), the operating system does not have to flush all entries out of the TLB whenever it switches processes. This cuts down on the number of TLB misses.

#### **Cache Operation**

The cache tags and control, like the TLB, are pipelined. At the same time the TLB entry is read, the cache tags are read, and the cache tag comparison is performed when the TLB tag comparison and protection check are performed, both for instructions and for data. However, the data RAMs (for both the instruction and the data caches) are not pipelined. Instead, the data RAMs for the instruction cache and the data cache are implemented using separate RAMs so that the access can span an entire cycle. This allows the use of larger, slower RAMs for the data, without affecting the cycle time. Otherwise, the cycle time would have to be long enough to allow reading the slower data RAM in a half cycle.

Like the TLB, the instruction cache and data cache are both direct mapped to minimize cycle time. They are as large as possible with current high-speed RAMs, thus keeping down miss rates. In addition, there are several features that allow the processor to keep running even though the cache is servicing a miss.

In the case of a data cache miss, the cache allows the processor to continue running until either the processor needs the data (from a load) or the processor executes another cache access. The first case is called a load/use

interlock, and occurs when the cache receives a load instruction for a particular register, and before the cache can supply the data, it receives another instruction that uses that target register. This is detected by comparing the load target for any load instruction in progress with the register fields of instructions being fetched, and causing the processor to freeze if there is a match. As soon as the data is returned to the processor, the interlock goes away and the processor can continue.

When there is a cache miss, the cache receives the data from main memory in a 4-word block, one word per cycle. To speed things up, as soon as the cache receives the requested data, it passes it through to the processor while it is also putting it into the cache. This allows execution to continue, even though the cache might still be servicing the miss.

When there is an instruction cache miss, the cache freezes the processor immediately, since it needs the instruction to continue. However, as soon as it receives the requested instruction from memory, it passes the instruction and the following instructions through to the processor to allow it to continue. The processor continues receiving the instructions straight from memory until either the end of the block is reached or the processor executes a taken branch. At the end of the block, the processor goes back to getting its instructions normally, from the cache. If the processor branches, the cache will freeze the processor until it finishes servicing the miss, then allow execution to continue. These optimizations improve performance by reducing the average cache miss penalty. Cache performance is measured by measuring the total miss penalty, which is the product of the miss rate and the penalty for each miss. The miss rate is minimized by making the cache as large as possible. The miss penalty is minimized by allowing the processor to execute whenever possible, even during cache miss servicing.

HP Precision Architecture allows a somewhat simpler cache than would otherwise have been possible, by putting the burden on software to keep the instruction and data caches consistent with each other and with any I/O being performed. The architecture provides cache flush and purge instructions, which software can use to guarantee that the copy in memory is up to date. Thus, the hardware does not have to check for a program modifying instruc-

Fig. 6. TLB pipeline.

tions, or whether DMA is accessing data that is currently in the cache.

#### **Performance**

Since this machine was the first HP Precision Architecture machine, we thought that it should be instrumented for hardware performance measurements. Thus the analysis interface card was born. This card is a coprocessor, and it has two functions. First, it depipes the instructions and presents the data to a frontplane interface to a logic analyzer. It can show three 32-bit buses and some control signals to the analyzer. The three buses can be chosen to show the instruction address, instruction, either source register, the ALU result, the load/store address, or the load/store data. Control signals indicate whether the instruction was executed or nullified, or if a taken branch or a trap occurred.

The analysis interface card and a disassembler for the HP 64000 Logic Development System were used extensively for both hardware and software debugging. The interface card was also used to take instruction traces for running performance simulations for other machine organizations.

The other function of the analyzer card is to collect performance statistics. It contains five 32-bit counters. Three of the counters can each count one of 32 predefined events. The other two counters form a pair, only one of which is readable by the processor. This pair of counters can count one of the 32 events in four ways: simple counting (like the other three), maximum duration of the event, number of times the event duration exceeds a threshold, or event occurrences masked by a one-zero-don't care comparator on one of the CPU buses. For example, the data cache miss rate can be measured by having one counter count data cache accesses and another count data cache misses. These statistics helped confirm the results of the cache and TLB simulations that were used to make trade-offs when the machine was being designed.

Events that can be counted are:

- Cycles

- Fetched instructions

- Executed instructions

- Loads

- Stores

- Branches taken

- Branches not taken

- Branches nullifying next instruction

- Arithmetic operations nullifying next instruction

- All architectural nullified instructions

- All nullified instructions

- External interrupts

- Traps

- Instruction cache misses

- Data cache misses

- Dirty data cache misses

- Instruction cache accesses

- Data cache accesses

- Instruction TLB misses

- Data TLB misses

- Instruction TLB accesses

- Data TLB accesses

- I/O accesses

- Load/use interlocks

- Cache wait cycles

- Coprocessor wait cycles

- Interlock and wait cycles

- Time spent at privilege level 0, 1, 2, or 3

- Time spent with interrupts off

- Time spent in virtual code space

- One write port interlocks.

#### **MIPS Calculations**

A frequently used measure of raw CPU power is millions of instructions per second, or MIPS. The MIPS rating of a computer is calculated as one over the cycle time times the cycles per instruction:

$$MIPS = \frac{1}{\text{cycle time } (\mu s) \times CPI}$$

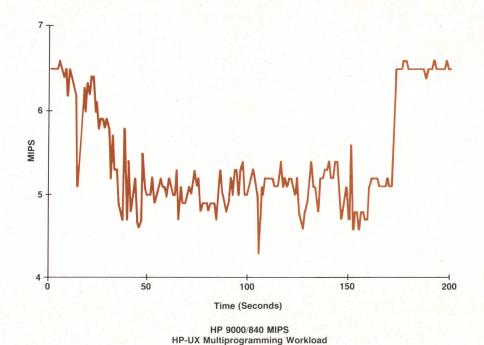

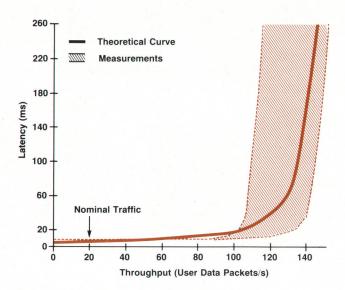

MIPS ratings are a good measure of performance when comparing machines with the same computer architecture, but can be misleading when comparing different architectures, since one architecture may take fewer instructions to complete the job than another. The best way to compare machines is to run the same application on both machines. Even on machines with the same architecture, the MIPS rating is calculated using a standard instruction mix or measured when running a standard jobstream. If the application differs from the standard then the MIPS rating might not be a good predictor of performance when running the application. The instantaneous MIPS rate of a computer is quite variable, as can be seen from Fig. 7, so any MIPS number quoted is only a long-term average. MIPS rates vary with the job executed and with time. MIPS ratings also have the drawback of not taking into account operating system efficiency, compiler efficiency, or I/O system efficiency. Therefore, MIPS is not a good metric for predicting applications performance on systems running different operating systems.

Cycles per instruction, or CPI, is the key measurement of how well a CPU uses its available power. Ideally, one instruction per cycle will be executed, so the CPI will be one. Calculating the CPI is straightforward: sum up the product of the penalties and their frequency, and add one:

$$CPI = 1 + \sum P_i F_i$$

There are two ways of minimizing the CPI: reduce the penalty  $(P_i)$  or reduce the frequency  $(F_i)$ .

#### Model 840 MIPS

For the HP 9000 Model 840 and HP 3000 Series 930 Computers, the cycle time is 125 ns. If there were no penalties, all instructions would take one cycle (CPI = 1), so the maximum possible performance is 8 MIPS.

The measured MIPS rate for the Model 840 varies from about 3.5 to 8 MIPS with an average of 4.5 to 5. (Fig. 7 shows measured performance during typical operation.)

The MIPS rating for the Model 840 can be calculated using the statistics gathered with the analysis interface card described above. First, there are nullified instructions. This happens when the compiler can't schedule a branch, and

when an arithmetic instruction skips on a condition. About 7% of all instructions are branches specifying nullify. About 2% of instructions are conditional skips that are taken. The load/use interlock happens when a load instruction is followed by an instruction that uses the data returned. About 14% of the instructions have this interlock. As the optimizing compiler improves, these numbers should go down. The Model 840 has an interlock that most HP Precision Architecture machines won't have: the one write port interlock. Since the load instruction result comes back one cycle after the load is executed, the architecture expects the register files to be able to write two results at the same time, one from the load instruction, and one from the ALU. The Model 840/Series 930 register file is built from static RAMs and can only store one result at a time. If a load instruction is followed by an instruction that stores a result, there will be a one-cycle interlock. This happens on about 8% of instructions.

Every instruction has the possibility of missing the Icache. Nullified instructions are fetched, so they can miss the I-cache also. The I-cache miss rate is about 3% and the miss penalty is 5 to 8 cycles with an average of about 7. The contribution to the CPI can be calculated by multiplying the miss rate (0.03) times the penalty (7) times the frequency of access (1.09). The frequency of access is 1.09 because for every one access per executed instruction, there is 0.09 access (9%) because of nullified and skipped instructions. This makes the CPI contribution 0.23 (see "Cache Performance," below). Every instruction can also miss the I-TLB. TLB misses cause a trap and are handled in software. This software is not doing any useful work so it is not counted as instructions executed for calculating MIPS. The miss handler is about 40 instructions and takes an average of about 70 cycles. The I-TLB miss rate is about 0.05%, so the CPI contribution is about 0.04 (0.0005 times 70.) Load and store instructions can miss the D-cache and the D-TLB. Loads are about 25% of the instruction mix and stores are

about 15%. A D-cache miss can cost anywhere from 1 to 15 cycles with an average of about 8. The D-cache miss rate is about 3%. The D-TLB miss rate is about 0.1%. The D-cache contribution to the CPI is about 0.1, and the D-TLB contribution is about 0.03. There is also a CPI contribution from flushing the cache for I/O. This is another function that most machines do in hardware, so it should not be counted in the instructions executed. The contribution to the CPI is about 0.04. The CPI is therefore:

| Basic instruction | 1.00 |

|-------------------|------|

| Nullify           | 0.09 |

| Load/use          | 0.14 |

| One write port    | 0.08 |

| I-cache miss      | 0.23 |

| I-TLB miss        | 0.04 |

| D-cache miss      | 0.10 |

| D-TLB miss        | 0.03 |

| I/O cache flush   | 0.04 |

|                   |      |

| Total CPI         | 1.75 |

This gives 4.57 MIPS as the calculated performance.

#### **Cache Performance**

Looking at the numbers in the preceding section, we can easily see that the cache is the major contributor to the CPI on this machine.

The function of a cache is to make the memory look faster by remembering recent memory accesses in the hope that they will be used again. Most programs have some sort of locality, that is, memory references in the recent past are likely to be used again in the near future. If this were not true, the cache would not work.

Caches normally take some amount of time, usually one cycle, to fetch data. This is how high performance is achieved; memory normally takes more than one cycle. Of concern are the less frequent cases when the cache takes

Fig. 7. HP 9000 Model 840 measured performance in millions of instructions per second (MIPS) during a typical operating period of 200 seconds.

more than one cycle to return the needed data. An example of this is when a piece of data is used for the first time. It cannot be in the cache, and must be fetched from memory. It is these less frequent cases that determine cache (and processor) performance.

The largest, and frequently only, penalty associated with caches is the miss penalty. It is the time the cache requires to get information (data or instructions) from memory. The cache needs to start a memory transaction, get the data back, and save it. All this time is counted as the miss penalty.

#### **Effects of Separate Caches**

The processor is capable of fetching an instruction every machine cycle, and some of these cycles, about 40%, also require a data cache reference. To prevent a large CPI increase (about 0.4), it is necessary to use the instruction and data caches during the same cycle. If the caches are combined (instruction and data cache are the same), the cache must be accessed twice per cycle. This becomes difficult to do with large caches, because the RAMs are just not fast enough. Splitting the cache into an instruction cache and a data cache allows both caches to be used in the same cycle without making them faster.

To prevent thrashing (excessive cache missing), a combined cache should also be at least two-way (two-set) associative. However, multiway associativity also slows down the cache, making it more difficult to build. Splitting the cache also eliminates this problem.

The decision to have separate instruction and data caches allowed us to use a large cache; a 128K-byte combined cache would have been difficult and expensive to build. The split cache does have a slightly lower hit rate than the combined cache, but this presented less of a problem than alternative cache organizations.

The cache is direct mapped, which means that each virtual address has exactly one place it can go in the cache. This is also known as a one-way associative cache. In twoway or four-way associative caches, a single virtual address can go in two or four places in the cache. Any number of ways can be built, but the expense is great, so normally, two-way or four-way associativity is used. Since each virtual address can go in more than one spot, there is less likely to be a conflict between two addresses. Thus the miss rate of the cache is lower. Simulations of the Model 840/Series 930 cache show that the miss rate would be about 40% lower if a four-way associative cache had been used. But this would have cost nearly four times as much in hardware, and would have required an increase in the cycle time of the machine, since the cache access takes longer when the cache must determine which way (set) contains the data. The benefits did not seem commensurate with the cost.

#### Write-Through versus Write-To

When the processor writes to the cache, the cache can do the write to memory at once (a write-through cache), or it can save the data and do the write to memory later (a write-to cache). The write-through cache has the benefit of always having a correct copy of the data in memory, something nice for I/O. A write-to cache reduces the bus traffic

considerably, since only a small number of writes generate a bus transaction.

Keeping the memory up to date is a problem that HP Precision Architecture leaves to software. That removes most of the additional complexity normally associated with the hardware on a write-to cache, and made the choice of a write-to cache clear.

Caches are something that software has traditionally not been able to control. But HP Precision Architecture provides explicit instructions for the software to maintain the caches. These are the purge and flush instructions, and all their variations. A purge removes the information from the cache without saving anything. A flush does the same, except that it writes the contents back into memory (for a write-to cache) before destroying it. The instructions come in two flavors, one for the instruction cache and one for the data cache. There is no purge instruction cache instruction, since a program can never write to (change) the instruction cache.

Why does this make a difference for performance? The explicit purge and flush instructions take time to execute. Traditionally this time has not been required. But the hardware complexity is significantly less, and therefore we can build faster caches. Although it is difficult to measure, we believe that the cost of the explicit instructions is less than the performance gain from the simplicity of the design.

Memory transactions in the Model 840/Series 930 processor occur on the MidBus, and are 16-byte (4-word) reads and writes, named READ16 and WRITE16. After a cache miss, the bus states are:

| WRITE16      |

|--------------|

| (cache miss) |

| Address      |

| Dead Cycle   |

| Data 0       |

| Data 1       |

| Data 2       |

| Data 3       |

| Tristate     |

|              |

|              |

The basic bus cycle is the same as the processor's, 125 ns. Two things are key: the latency and the data rate. The latency is how long it takes to get the first word of data back (time from address to first data). The data rate is how fast the data comes back once it starts going. If the latency is high, the miss penalty will be high. It may be best to load more data in that case. If the data rate is the same as the instruction rate, bypassing the instruction cache can make a lot of sense. In general, the latency is largely determined by the bus and the memory (dynamic RAMs) used. It is hard to reduce. The data rate is also determined by the bus, but it is easily controlled by adjusting the bus width and cycle time.

#### **Effects of Bypassing**

Cache line bypassing is the concept of using the instructions or data as they are loaded into the cache, rather than waiting for the cache miss to finish. This reduces the penalty of the cache miss, but it has a few problems, too. In the Model 840/Series 930 processor, about three-quarters

of the instruction cache misses occur on the first word of a line, and the rest are evenly distributed among the other three words. The instruction cache penalty on the Model 840/Series 930 processor is 9 cycles with no bypassing, but is from 5 to 8 cycles if bypassing is used. The effective miss penalty is calculated by summing 75% of 5, 8% of 6, 8% of 7, and 8% of 8. This comes out to 5.12, much better than 9.

When actually measured, the effective miss penalty is 5.35, close to the calculated value. Comparing these numbers (still incomplete) at this point gives a CPI contribution of 0.16 with bypassing, and 0.27 without bypassing. These numbers were calculated by multiplying the I-cache miss rate (assumed 3%) by the respective miss penalties.

Some other things must be considered. If the processor is not executing the instructions in the same order and at the same speed as they are coming into the cache, the analysis breaks down. The Model 840/Series 930 processor is capable of doing this, but there are two important exceptions: a processor freeze and a taken branch. If the processor freezes for any reason other than the instruction cache miss, the instructions coming from memory are now too early for the processor. In the case of a branch that is taken, the instructions coming from memory simply are not the proper instructions. In both cases, the processor is refrozen and the instructions from memory are ignored. However, this is what happens anyway; there is no additional penalty for bypassing. On the Model 840/Series 930 processor, this refreeze adds 1.90 cycles to the effective I-cache miss penalty. This brings the total miss penalty to 7.25. Recalculating the CPI, a bypassed I-cache adds 0.22, while no bypassing adds 0.27. The processor performance gain by using bypassing is 0.05 CPI multiplied by 8 raw MIPS, or 0.40 MIPS, about a 10% gain.

Bypassing is also done on the data cache. Here it is not nearly so important. Since the cache can only handle one cache operation at a time and the cache operation is not finished until the miss has been handled, bypassing only works for one access per line. The CPI contributions, calculated in a similar way as above (but more complicated) are 0.10 for bypassing versus 0.13 for no bypassing. Bypassing is done on the data cache simply because it was easy to implement. The logic existed for the instruction cache (where it makes a larger difference), and was easy to multiplex between the two caches.

The following table summarizes the bypass and nobypass performance calculations.

|         | no<br>bypass | bypass | diffe | erence |

|---------|--------------|--------|-------|--------|

|         | (CPI)        | (CPI)  | (CPI) | (MIPS) |

| I-cache | 0.27         | 0.22   | 0.05  | 0.40   |

| D-cache | 0.13         | 0.10   | 0.03  | 0.24   |

Bypassing has one other problem. If the bus supports retries (a third party requests that the current bus transaction be ignored and tried again), the retry must be known before the first data word is used. Normally this means that the retry signal must be present with or before the first data word. Because of control complexity, the retry signal must be present on the MidBus one cycle before the first

data word in the Model 840/Series 930 processor.

#### Critical Word First, Line Size, and Cache Size

Critical word first is an idea that only makes sense with cache line bypassing. It is the idea of rearranging the data on the transaction so that the needed word comes first, and the rest come later. For example, if the second word (word 1) is needed first, the memory would return the data in this order: word 1, word 2, word 3, then word 0. Taking a look back at the miss penalty for the instruction cache (5.35), we can see that this doesn't make a lot of sense. A miss penalty of 5 is the best we could do. Critical word first also potentially introduces a penalty on the 32-byte memory transactions, a discussion of which is beyond the scope of this paper. The Model 840/Series 930 cache and memory do not support critical word first.

Caches load one line at a time from memory. How big should this line be? Typically, the larger the line size, the more efficiently it can be loaded from memory. But with large lines, it is more likely that words will be loaded that will never be used. Since the instruction cache is normally used in a regular way, it benefits more from a large line size than the data cache. The Model 840/Series 930 processor uses a line size of 16 bytes (4 words) for both the instruction and the data caches. A line size of eight words would have been better for the instruction cache, but would have been difficult to implement since the Model 840/Series 930 has combined, pipelined cache tags.

Determining how big to build a cache is sometimes difficult. The larger the cache, the lower the miss rate will be, as long as you stay in the same global address space. Some processors do not have a single address space large enough to handle multiprocessing. Operating systems can get around this problem by flushing the TLB on process switches. Sometimes it is necessary to flush the cache, too. If the processor must flush the cache on a process switch, there comes a point where building larger caches may not help, and may even hurt system performance. This would put a practical limit on the size of TLBs and caches in such systems. The larger they are, the longer they take to flush. Also, the larger they are, the less likely they are to be fully used before a process is switched out again. HP Precision Architecture solves this problem by having a single large address space. All processes share this common address space, and no flushing needs to be done on either the TLB or the cache during process switches. With HP Precision Architecture, larger caches are always higher-performance, as long as the cycle time is not affected.

#### **Floating-Point Coprocessor**

In HP Precision Architecture, floating-point operations are handled by a coprocessor. This coprocessor runs concurrently with the main CPU and has the sole job of supporting floating-point arithmetic. Floating-point arithmetic is well-suited for a coprocessor because it involves calculations that require multiple cycles to perform. This means that although the floating-point instruction occupies one position in the instruction stream, the main CPU can receive and execute subsequent non-floating-point instructions concurrently with subsequent cycles of the floating-

point instruction.

As a true coprocessor, the floating-point board decodes its own instructions. It also has its own set of sixteen 64-bit registers. Data is sent to the floating-point board by loads from the cache and results are retrieved via stores to the cache. The floating-point operations are performed according to the IEEE standard for binary floating-point arithmetic.

The floating-point board is not equipped to handle all floating-point operations required, nor all floating-point number values. When an unsupported operation or data value is detected, the floating-point board indicates this fact to the main CPU, which then handles the operation in software. The occurrence of these operations requiring software is rare and does not significantly affect performance, but does ensure that the IEEE standard is completely satisfied.

#### **Overlapped Processing**

During the initial investigation for the floating-point board, a simple design was considered, which did not allow overlap of any type of floating-point instuctions. However, several types of floating-point applications (e.g., matrix multiply, vector sum,  $3\times 3$  graphics transformation, etc.) were examined and estimates of performance were made. It quickly became apparent that the initial design did not meet the performance goals. Furthermore, in most of the applications examined, allowing nonconflicting floating-point loads and stores to be processed while floating-point operations (flops) were being executed increased the performance enough to meet the goals. Therefore, the floating-point coprocessor implements this capability.

Once the capability of the board was decided, the design was implemented in a simple and straightforward manner. It was determined that microcode would be used to execute flops, while floating-point loads and stores would be implemented completely in hardware. A proprietary HP floating-point add, multiply, and divide chip set used in the HP 9000 Model 550 was selected to do the floating-point calculations. Also, a special assembler was written to convert the source microcode into a listing file and a burn file, with the latter being used to program the microcode PROMs.

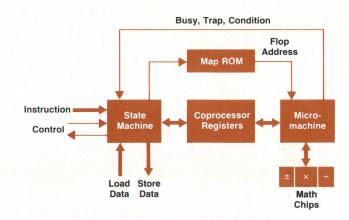

The design choices led to the partitioning of the floating-point board into two distinct parts, the micromachine and the state machine (see Fig. 8). These two control pieces share a common data bus and both have access to the register file. They share these data paths on a time basis, with each in control for half of the 125-ns cycle time. The state machine does all of the interfacing with the main CPU and provides control for floating-point loads and stores. It also dispatches the micromachine to execute flops and signals the main CPU when traps or freezes are necessary.

The organization of the floating-point board into these two distinct control blocks is well-suited for allowing floating-point loads and stores to be processed while flops are in progress. When the state machine receives a floating-point load or store it simultaneously determines whether the micromachine is busy, and if so, determines whether the new load or store conflicts with the flop in progress by accessing a floating-point register used in the flop. If

there is no conflict, the state machine processes the floating-point load or store immediately; otherwise, it waits until the flop is completed.

#### **Self-Test**

A full self-test strategy is built into the floating-point board design. A special, machine dependent instruction was created, which when executed causes the micromachine to perform a detailed diagnostic test of the floating-point board. This test signals pass or error conditions by setting bits in one of the floating-point registers. It also puts the one's complement of these bits into another register so that the validity of the information in the first register can be verified. Also included in the self-test strategy is the ability of the main CPU to distinguish between a malfunctioning floating-point board and the lack of a floating-point board in the system.

At power-up, a self-test is run on the floating-point board. The test includes the microcoded self-test as well as one instruction of each type of floating-point operation to ensure that the board is performing correctly. If this is determined to be the case, then the system is configured with the floating-point board enabled. If this is not the case, an error is signaled during initialization. The floating-point card can then be removed and the system rebooted without the floating-point board enabled. Then all floating-point operations are performed in software.

#### **Development Methods**

Once the floating-point hardware was solid enough to run in a system environment, a software test package was written to aid in catching numerical errors. This package allows us to test any flop with any operands. It also offers a pattern mode, during which operands are generated in a user-controlled pattern and continually used in flops. It functions by checking results received from the floating-point hardware with results derived from software floating-point routines. During development, if discrepancies were found between the two results, the operands, operation, and results were logged to an error file. In the pattern mode of operation, this software package caught a few numerical flaws both in the floating-point hardware and in the software floating-point routines. The mistakes in the software floating-point routines were equally important to correct

Fig. 8. Floating-point coprocessor block diagram.

because in the absence of hardware, they would be used to do the calculations.

To get the maximum performance from the floating-point board, the compiler groups and especially those connected with the optimizer were brought into the design process in the early stages. They were given information on how long each flop took to execute and what constitutes a conflicting load or store versus a nonconflicting load or store. Using this information along with their knowledge of the operating characteristics of the main CPU, they altered their compilers and optimizers so that the instruction ordering and floating-point register allocation they generated would take the best advantage of the floating-point hardware that existed.

The inclusion of the floating-point coprocessor with the main CPU allows the hardware to be used in a technical environment. Its position in the system as a coprocessor enhances the overall system performance by allowing the CPU to do non-floating-point activities such as address generation and integer arithmetic while multicycle flops are in progress. The floating-point board's ability to do floating-point loads and stores concurrently with flops means that while one result is being calculated, previous results can be stored and operands for future flops can be loaded. In summary, the design of the floating-point board, its placement in the system, and its influence on the compilers and optimizers all serve to get the maximum technical performance from the technology used to implement the design.

#### **Memory System**

The Model 840/Series 930 memory system is designed to maximize performance by keeping the latency from address to first word as small as possible. All signals were potential critical path signals and had to be analyzed carefully to ensure that the timing goals were met. The memory strobe lines RAS and CAS were closely analyzed so that the skew was minimized.

The DRAMs are accessed using nibble mode so that a read operation can return a word of data every 125 ns after a latency period of 300 ns. The memory controller is implemented using TTL technology.

The memory system communicates with the processor and the I/O system through the MidBus, which is a synchronous high-speed bus. There is parity checking on the MidBus for the address, data, and control lines. The memory generates and checks parity on data reads and data writes to improve the reliability of the memory system.

The memory can be accessed in either 16-byte or 32-byte transactions. The 16-byte transaction takes seven cycles and the 32-byte transaction requires 13 cycles. The maximum memory bandwidth for 16-byte transactions is 18.285 Mbytes/s and for 32-byte transactions is 19.7 Mbytes/s.

At power-up it is necessary to initialize the memory controller. The architected control and status registers are visible to the software in the I/O address space. The boot code initializes the memory controller, setting up the physical memory's address range via MidBus I/O transactions to the I/O registers resident on the controller.

Each 8M-byte main memory module is physically located on two boards. The memory controller board contains three banks of DRAMs and the memory array contains five banks of DRAMs. One memory controller communicates with one memory array card. While this increases the manufacturing price compared to a product that extends the reach of the controller to many memory cards, it has the advantage of reducing latency, since fewer DRAMs are addressed and the address and data buses are shorter.

27 bits of the 32-bit physical address are used. This limits addressability to a 128M-byte physical space.

#### **Error Correction**

Error-correcting memory is standard. A 32-bit error-detection and correction (EDC) chip forms the basis of this circuitry. During a memory write operation, 32 bits of data are sent through the EDC logic, which generates seven checkbits. These are merged with 32 bits of data in the proper RAM bank. When a memory read operation occurs, these 39 bits are sent through the EDC logic, which internally regenerates what the seven checkbits should be and compares them to the checkbits that it actually got from the RAM bank. The result of this comparison is called a syndrome. The checkbits for each 32-bit pattern are chosen so that the syndrome reveals useful information about any errors that are detected. If the error is a single-bit error, the syndrome can be decoded to see which bit is wrong. The EDC does this and corrects the error. Multiple-bit errors are not correctable. The best that can be done is to detect their presence and interrupt the processor by pulling on the error signal on the MidBus.

#### **System Monitor Module**

The power system consists of several major components:

- Ac front-end power distribution unit

- 5-kVA isolation transformer

- Fan tray with four ac fans and backup battery

- Three 300W power supplies

- System monitor module

- Internal and external control panels.

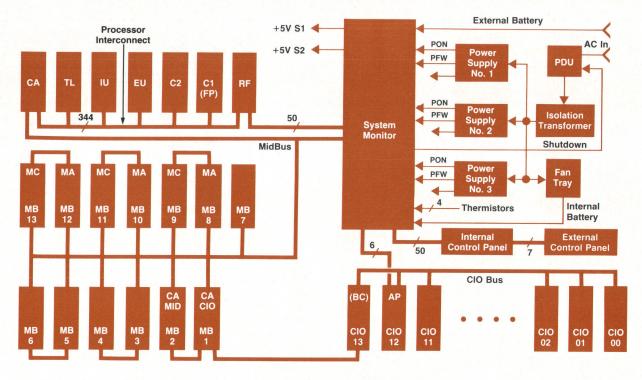

The relationship among these components is represented in the system block diagram, Fig. 9. The system monitor module serves as an interface between the power supply and the SPU boards. It generates secondary power (+5V S1 and +5V S2) to the CPU and memory boards, processes power-on and powerfail warning signals to the MidBus, terminates and arbitrates MidBus signals, monitors system temperature, and interfaces with the control panel and access port. It also includes some miscellaneous processor dependent hardware consisting of the time-of-day clock, stable storage, diagnostic switches, and an EPROM for processor dependent code.

The secondary power is generated by two dc-to-dc converters. In the normal mode of operation, the system monitor module converts +28V from two of the power supplies to +5.1V to supply up to six memory boards, or 24M bytes of memory. During the backup mode, the dc-to-dc converters take power from the 10V 10A backup battery. The battery can supply up to six memory boards for at least 15 minutes during a powerfail. An external battery connec-

Fig. 9. System diagram of the HP 9000 Model 840 and HP 3000 Series 930 Computers.

tor is provided if additional backup time is required. The battery enable switch is built into the ac circuit breaker on the power distribution unit. Another battery test switch on the power distribution unit can bypass the battery enable switch for powerfail testing.

The system temperature is monitored by four thermistors on the backplane. When an overtemperature situation occurs, the system monitor module turns on the yellow warning light and sets a flag to the CPU at 45°C inside the cabinet. At 60°C, the system monitor module trips the ac circuit breaker and shuts off all the power including battery backup.

The processor dependent hardware on the system monitor module communicates with the CPU via diagnostic instructions. The diagnostic instructions have access to the control-panel hexadecimal status displays, the time-of-day clock chip, the stable-storage CMOS RAM, and the diagnostic switches. The software can read from and write to these components via entry points in the processor dependent code. The clock chip and the stable-storage RAM are backed up by two lithium batteries on the system monitor module during powerfail. A parallel-to-serial interface converts 16 bits of hexadecimal display data serially to the access port to facilitate remote diagnosis.

#### **Acknowledgments**

Many people contributed to the hardware development of the Model 840/Series 930. The authors would particularly like to thank Lee Moncton for his guidance as our original project manager, Joe Mixsell for helping us keep the faith during the dark times, Paul Bliley and Chris Livingston for their technical assistance during all phases of the project, Darlene Harrell for prototyping work, Rose-

mary Kingsley for production documentation and making sure we always had parts when we needed them, Ken Robertson, Luann Piccard, and Bea Netter for the mechanical and industrial design, Al Hum, Randy Teegarden, and Tom Wylegala for production engineering, Jess Pawlak for supporting those first 36 systems, Jerry Everett and his people for supporting over 400 lab prototype and production prototype systems, Jim Finnell for the original cache design, Don Cross for the I/O channel design, Don Williamson for the original E-Unit design, Chuck Gebber, Tom Harms, and Albert Chun for their contributions to the floating-point board, Julie Wu, Tom Alexander, and Carl Woodard for taking over and maintaining the majority of the original CPU design, Bill Shellooe for his invaluable help in creating and maintaining our tools, and Cheryl Gressman and all of the people in the printed circuit design shop.

#### References

- 1. M.J. Mahon, et al, "Hewlett-Packard Precision Architecture: The Processor," *Hewlett-Packard Journal*, Vol. 37, no. 8, August 1986, pp. 4-21.

- 2. D.V. James, et al, "Hewlett-Packard Precision Architecture: The Input/Output System," *ibid*, pp. 23-30.

- 3. F.W. Clegg, et al, "The HP-UX Operating System on HP Precision Architecture Computers," *Hewlett-Packard Journal*, Vol. 37, no. 12, December 1986, pp. 4-22.

- 4. J.R. Busch, et al, "MPE XL: The Operating System for HP's Next Generation of Commercial Computer Systems," *Hewlett-Packard Journal*, to be published.

- 5. G. Buchanan, et al, "A Distributed Terminal Controller for HP Precision Architecture Computers Running the MPE XL Operating System," this issue.

# An Automated Test System for the First HP Precision Architecture Computers

Besides testing for proper operation, the system gathers specific failure information and generates summary statistics to be used in improving the manufacturing process.

by Thomas B. Wylegala, Long C. Chow, and Randy J. Teegarden

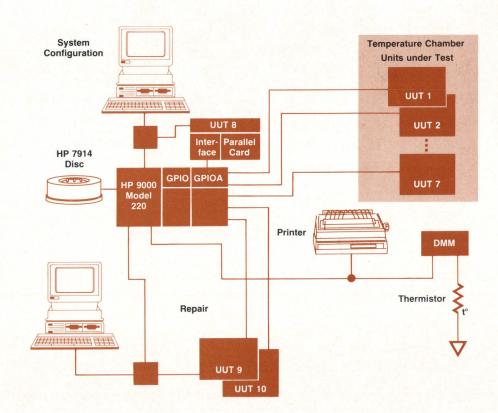

HE AUTOMATED TEST SYSTEM for the first computers of the HP Precision Architecture family can test up to ten HP 9000 Model 840 or HP 3000 Series 930 Computers simultaneously. Fig. 1 is a block diagram of the test system.

A Model 840/Series 930 Computer configured with two special boards can be connected to the test system via a cable. The test system then has the ability to load diagnostic programs into the Model 840/Series 930 and monitor the results of those tests. The host for the test system is an HP 9000 Model 220, but any HP 9000 machine that runs the HP-UX 5.1 operating system could serve as well.

#### **Key Features**

The Model 840/Series 930 computer contains 32K bytes of test code resident in ROM. This self-test code is executed whenever the computer is powered on or reset. There is a

need to supplement this test code with additional specialized test programs. Also, it is expensive to modify firmware based code, but easy to add a new test to the test system. Therefore, the test system provides the capability to download test programs into the memory of the computer under test and to initiate their execution.

The test system monitors the results of test execution and writes the status to a log file. This eliminates the need to have a human operator constantly observing the unit under test to judge whether the unit has passed. The test system collects the data elements that are critical to the success of the quality control program.

Little peripheral equipment is required to support the testing process. Without the test system, the minimum configuration to run diagnostics on Model 840/Series 930 processors includes a console and a disc for each unit under test. The peripherals for the testing of ten units would be

**Fig. 1.** Block diagram of the test system for HP 9000 Model 840 and HP 3000 Series 930 processors.

expensive and would consume valuable factory space.

Finally, the test system requires minimal cooperation from the unit under test. Even catastrophic self-test failures can be detected properly by the test system. It can even download test programs into a unit whose normal input/output channels are inoperable.

#### **Hardware Developed**

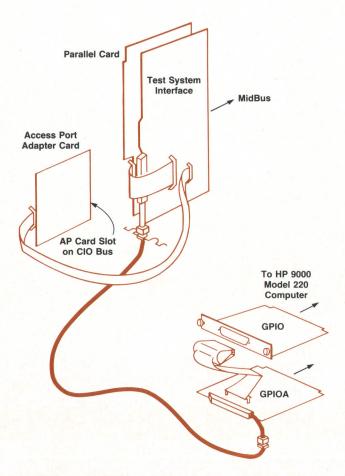

The communications interface between the test system and the unit under test is based on the link used to support the remote debugger (RDB),<sup>1</sup> so the test system is fully compatible with RDB. That link involves a 16-bit path between a GPIO card in the HP 9000 host and a parallel card in the Model 840/Series 930 under test. For the test system, two custom boards (called the test system interface and the GPIOA adapter) were designed to enhance the RDB link. The connections are shown in Fig. 2.

Many advantages accrue from inserting these two custom cards into the path. Signals can be transmitted reliably over distances up to 300 feet (versus 3 feet for the original link) using an EIA RS-422 differential interface. The system will work with both the new differential drive and the original single-ended drive versions of the parallel card. The test system interface also has access to signals on the access port card slot. These signals allow the test system to give the unit a hard reset and to receive the 16 bits of serial data sent to the access port card. These 16 bits of data,

Fig. 2. Parallel link configuration.

which on Model 840/Series 930 processors also appear on the LED status display, enable the unit under test to send messages to the test system even if a failure in the CIO channel adapter prevents communication via the console. Finally, the test system can determine when the unit under test has been powered on or off.

#### **Firmware Developed**

The I/O dependent code (IODC)<sup>2</sup> for the parallel card was written to make communications with the test system possible. The IODC contains a communications server which enables the Model 840/Series 930 to interpret the data being transmitted to it by the test system through the parallel card. When the boot information in the Model 840/Series 930's stable storage area indicates that a parallel card is to serve as the boot device, the communications server is launched after the self-test has completed.

#### **Software Developed**

The test system control software has a multiprocess structure. The main process, which is scheduled when the test system is initiated, contains the user interface. It maintains the status windows, updates the softkeys, and executes user commands. There is one p\_monitor process for each computer under test. These processes manage the communications with the units under test. Finally, there is a background process that performs periodic and intermittent tasks. The test system control software allows easy reconfiguration of each test station. Parameters that can be configured include the list of tests to be executed and the number of temperature cycles needed for test completion.

The test system allows diagnostic programs to be loaded into the computers under test. Developing these diagnostics was another challenge. Several sets of test programs were written. For example, there is an exerciser for the translation lookaside buffer (TLB) that verifies the proper operation of each field in every entry of the TLB. A total of 49 of the original architecture verification programs were adapted for use with the test system. These programs perform extensive testing of the arithmetic, logical, and branch instructions. The test programs obey some conventions to make the test system's job easier. For instance, the programs use the access port interface path to transmit error codes to the test system to indicate failures or a pass code to indicate when the test has completed successfully. All of the tests written for the Model 840/Series 930 use the data FFFF in hexadecimal to signal success and preface a failure message with the data DEAD. The Model 840/Series 930 tests also compute a checksum on their instruction text to ensure that the program was downloaded correctly.

#### **Relation to the Manufacturing Process**

Model 840/Series 930 boards are subjected to three levels of testing during their manufacture. First is a board-level in-circuit test on the HP 3065 Board Test System.<sup>3</sup> This test screens out most process related problems, such as bent pins and solder bridges. Next, boards are grouped into sets, installed into backplanes, and subjected to functional tests in a temperature chamber. The temperature chamber continuously cycles from 0 to 55°C with a period of two hours. This test detects temperature-sensitive component